# **Doctorat ParisTech**

# THÈSE

pour obtenir le grade de docteur délivré par

# **TELECOM** ParisTech

## Spécialité « Informatique »

présentée et soutenue publiquement par

## **Clémentine MAURICE**

le 28 octobre 2015

# Fuites d'information dans les processeurs récents et applications à la virtualisation

Directeurs de thèse :

**Aurélien FRANCILLON** Christoph NEUMANN Co-encadrement de la thèse : **Olivier HEEN**

Jury

M. Thomas JENSEN, Directeur de recherche, Inria Rennes, France

M. Gildas AVOINE, Professeur, IRISA et INSA Rennes, France

M. Jean-Pierre SEIFERT, Professeur, TU Berlin, Allemagne

M. Stefan MANGARD, Professeur, TU Graz, Autriche

M. Pierre PARADINAS, Professeur, CNAM, Paris, France

**TELECOM ParisTech**

école de l'Institut Télécom - membre de ParisTech

Président de jury Rapporteur Rapporteur Examinateur Examinateur

## **Information Leakage on Shared Hardware** Evolutions in Recent Hardware and Applications to Virtualization

**Clémentine Maurice**

A doctoral dissertation submitted to: Télécom ParisTech

Advisors: **Aurélien Francillon**, Eurecom, Sophia Antipolis, France **Christoph Neumann**, Technicolor, Rennes, France **Olivier Heen**, Technicolor, Rennes, France

Jury: Thomas Jensen, Inria Rennes, France Gildas Avoine, IRISA and INSA Rennes, France Jean-Pierre Seifert, TU Berlin, Germany Stefan Mangard, TU Graz, Austria Pierre Paradinas, CNAM, Paris, France

President Reviewer Reviewer Examiner Examiner

October 2015

# Contents

| Co | onten  | ts       |                                            | i    |

|----|--------|----------|--------------------------------------------|------|

| Ré | ésum   | é        |                                            | vii  |

| Al | ostrac | zt       |                                            | ix   |

| Ac | cknov  | vledgn   | rents                                      | xi   |

| Fo | orewo  | rd       |                                            | xiii |

| 1  | Intr   | oductio  | on                                         | 1    |

|    | 1.1    | Conte    | xt                                         | 1    |

|    | 1.2    | Proble   | em statement                               | 2    |

|    | 1.3    | Contr    | ibutions                                   | 3    |

|    | 1.4    | Orgar    | nization of the thesis                     | 5    |

| 2  | Stat   | e of the | e art                                      | 7    |

|    | 2.1    | Archi    | tecture of an x86 system                   | 7    |

|    |        | 2.1.1    | СРИ                                        | 7    |

|    |        |          | 2.1.1.1 Data cache                         | 9    |

|    |        |          | 2.1.1.2 Instruction cache                  | 12   |

|    |        |          | 2.1.1.3 Branch prediction unit             | 12   |

|    |        | 2.1.2    | Memory                                     | 13   |

|    | 2.2    | Hardy    | ware virtualization                        | 13   |

|    |        | 2.2.1    | СРИ                                        | 14   |

|    |        | 2.2.2    | Memory                                     | 15   |

|    |        | 2.2.3    | I/O devices                                | 16   |

|    |        | 2.2.4    | Attack surface of the virtualization layer | 17   |

|    |        |          | 2.2.4.1 Hypervisor                         | 17   |

|    |        |          | 2.2.4.2 Device emulator                    | 18   |

|   |     |        | 2.2.4.3    | Direct device assignment                | 18 |

|---|-----|--------|------------|-----------------------------------------|----|

|   | 2.3 | Cover  | t and side | e channels on shared resources          | 18 |

|   |     | 2.3.1  | Achievi    | ng and detecting co-residency           | 19 |

|   |     | 2.3.2  |            | surface of an x86 processor             | 20 |

|   |     |        | 2.3.2.1    | Data and instruction cache              | 20 |

|   |     |        | 2.3.2.2    | Branch prediction unit                  | 21 |

|   |     |        | 2.3.2.3    | Arithmetic logic unit                   | 21 |

|   |     | 2.3.3  | Attack s   | surface of the memory and memory bus    | 22 |

|   |     |        | 2.3.3.1    | Memory deduplication                    | 22 |

|   |     |        | 2.3.3.2    | Memory bus                              | 22 |

|   | 2.4 | The ca | se of the  | data cache of x86 processors            | 23 |

|   |     | 2.4.1  |            | riven attacks                           | 23 |

|   |     | 2.4.2  | Trace-dr   | riven attacks                           | 24 |

|   |     | 2.4.3  | Access-    | driven attacks                          | 24 |

|   |     | 2.4.4  | Beyond     | cryptographic side channels             | 26 |

|   |     | 2.4.5  | Evolutio   | ons of cache attacks                    | 27 |

|   |     |        | 2.4.5.1    | From single-core to muti-core CPUs      | 27 |

|   |     |        | 2.4.5.2    | From native to virtualized environments | 28 |

|   |     |        | 2.4.5.3    | From shared to non-shared memory        | 28 |

|   |     | 2.4.6  | Timing     | measurements                            | 29 |

|   |     | 2.4.7  | Counter    | rmeasures                               | 29 |

|   |     |        | 2.4.7.1    | Architecture or microarchitecture level | 29 |

|   |     |        | 2.4.7.2    | Operating system or hypervisor level    | 30 |

|   |     |        | 2.4.7.3    | Application level                       | 31 |

|   | 2.5 | Inform | nation lea | kage on GPU memory                      | 33 |

|   |     | 2.5.1  | Archite    | cture                                   | 33 |

|   |     | 2.5.2  | Program    | nming model                             | 34 |

|   |     | 2.5.3  | Offensiv   | ve usage of GPUs                        | 34 |

|   |     |        | 2.5.3.1    | The GPU as the subject of attacks       | 34 |

|   |     |        | 2.5.3.2    | The GPU as a medium for attacks         | 35 |

|   |     | 2.5.4  | Defensi    | ve usage of GPUs                        | 35 |

|   | 2.6 | Conclu |            |                                         | 36 |

| _ | _   |        | _          |                                         |    |

| 3 |     |        |            | mplex addressing: C5 covert channel     | 37 |

|   | 3.1 |        |            |                                         | 37 |

|   | 3.2 |        |            | dressing uncertainty                    | 38 |

|   | 3.3 |        |            | 5                                       | 40 |

|   | 3.4 | Sende  |            |                                         | 41 |

|   | 3.5 |        |            |                                         | 43 |

|   | 3.6 | Evalua | ation      |                                         | 45 |

|   |            | 3.6.1 Testbed                                                    | 45         |

|---|------------|------------------------------------------------------------------|------------|

|   |            | 3.6.2 Native environment                                         | <b>1</b> 6 |

|   |            | 3.6.3 Virtualized environment                                    | 47         |

|   | 3.7        | Discussion                                                       | <b>1</b> 8 |

|   | 3.8        | Countermeasures                                                  | 51         |

|   |            | 3.8.1 Hardware countermeasures                                   | 51         |

|   |            | 3.8.2 Software countermeasures                                   | 52         |

|   | 3.9        | Related work                                                     | 52         |

|   | 3.10       |                                                                  | 54         |

| 4 | Reve       |                                                                  | 55         |

|   | 4.1        |                                                                  | 55         |

|   | 4.2        | 1                                                                | 56         |

|   | 4.3        |                                                                  | 57         |

|   | 4.4        |                                                                  | 59         |

|   |            |                                                                  | 59         |

|   |            | 4.4.2 Manually reconstructing the function for Xeon E5-2609 v2 6 |            |

|   |            | 8                                                                | 51         |

|   | 4.5        |                                                                  | 53         |

|   |            | 0                                                                | 53         |

|   |            |                                                                  | 55         |

|   | 4.6        |                                                                  | 56         |

|   |            | 0 1 5                                                            | 56         |

|   | 4 7        |                                                                  | 67         |

|   | 4.7        |                                                                  | 58         |

|   | 4.8        | Conclusions and perspectives                                     | 59         |

| 5 |            | 0                                                                | 71         |

|   | 5.1        |                                                                  | 71<br>72   |

|   | 5.2<br>5.2 |                                                                  | 73         |

|   | 5.3        |                                                                  | 73         |

|   |            |                                                                  | 73         |

|   |            | 1                                                                | 74         |

|   |            | 0                                                                | 74<br>74   |

|   | 5.4        | 0                                                                | 75         |

|   | 5.4<br>5.5 | 1 1                                                              | 77         |

|   | 5.5        |                                                                  | 77         |

|   |            |                                                                  | 78         |

|   |            |                                                                  | 79         |

|   |            |                                                                  |            |

|    | 5.6  | Access         | sing memory through PCI configuration space             | 79         |

|----|------|----------------|---------------------------------------------------------|------------|

|    |      | 5.6.1          | Native environment                                      | 80         |

|    |      | 5.6.2          | Virtualized and cloud environment                       | 81         |

|    | 5.7  | Count          | ermeasures                                              | 82         |

|    |      | 5.7.1          | GPGPU runtimes                                          | 82         |

|    |      | 5.7.2          | Hypervisors and cloud providers                         | 82         |

|    |      | 5.7.3          | Defensive programming                                   | 83         |

|    | 5.8  | Relate         | d work                                                  | 83         |

|    | 5.9  |                | usions and perspectives                                 | 84         |

| 6  | Con  | clusion        | is and future directions                                | 85         |

|    | 6.1  | Contri         | butions                                                 | 85         |

|    | 6.2  | Future         | e directions                                            | 86         |

|    |      | 6.2.1          | Attack techniques                                       | 87         |

|    |      | 6.2.2          | Defense techniques                                      | 87         |

|    |      | 6.2.3          | Expanding knowledge of CPU internals                    | 88         |

| Aŗ | penc | lices          |                                                         | 88         |

| A  | Rési | ımé en         | français                                                | 89         |

|    | A.1  | Introd         | uction                                                  | 89         |

|    |      | A.1.1          | Contexte                                                | 89         |

|    |      | A.1.2          | 1                                                       | 90         |

|    |      | A.1.3          | Contributions                                           | 90         |

|    |      | A.1.4          | Organisation de la thèse                                | 92         |

|    | A.2  | Conto          | urner l'adressage complexe : le canal caché C5          | 93         |

|    | A.3  | Rétro-         | ingénierie de l'adressage du dernier niveau de cache    | 94         |

|    | A.4  | Fuites         | d'informations sur la mémoire des GPUs                  | 95         |

|    | A.5  | Travaı         | 1x futurs                                               | 96         |

|    |      | A.5.1          | Nouvelles attaques                                      | 96         |

|    |      | A.5.2          | Contre-mesures                                          | 97         |

|    |      | A.5.3          | Élargir les connaissances du fonctionnement interne des |            |

|    |      |                | CPUs                                                    | 97         |

| B  | Accu | arate ti       | ming measurements                                       | 99         |

| C  | MSI  |                | s for reverse-engineering the addressing function       | 101        |

|    | C.1  | Xeon (         | CPUs                                                    | 101        |

|    |      | C.1.1<br>C.1.2 | Monitoring session                                      | 101<br>102 |

|    |      |                |                                                         |            |

| C.2       | C.1.4<br>Core C<br>C.2.1 | MSR addresses and values for Xeon Ivy Bridge CPUsMSR addresses and values for Xeon Haswell CPUsCPUsMonitoring sessionMSR addresses and values | 104<br>105<br>105 |

|-----------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| List of I | igures                   |                                                                                                                                               | 107               |

| List of 7 | <b>Fables</b>            |                                                                                                                                               | 109               |

| Bibliog   | raphy                    |                                                                                                                                               | 111               |

# Résumé

Dans un environnement virtualisé, l'hyperviseur fournit l'isolation au niveau logiciel, mais l'infrastructure partagée rend possible des attaques au niveau matériel. Les attaques par canaux auxiliaires ainsi que les canaux cachés sont des problèmes bien connus liés aux infrastructures partagées, et en particulier au partage du processeur. Cependant, ces attaques reposent sur des caractéristiques propres à la microarchitecture qui change avec les différentes générations de matériel. Ces dernières années ont vu la progression des calculs généralistes sur processeurs graphiques (aussi appelés GPUs), couplés aux environnements dits *cloud*. Cette thèse explore ces récentes évolutions, ainsi que leurs conséquences en termes de fuites d'information dans les environnements virtualisés. Premièrement, nous investiguons les microarchitectures des processeurs récents. Notre première contribution est C5, un canal caché sur le cache qui traverse les coeurs d'un processeur, évalué entre deux machines virtuelles. Notre deuxième contribution est la rétro-ingénierie de la fonction d'adressage complexe du dernier niveau de cache des processeurs Intel, rendant la classe des attaques sur les caches facilement réalisable en pratique. Finalement, dans la dernière partie nous investiguons la sécurité de la virtualisation des GPUs. Notre troisième contribution montre que les environnements virtualisés sont susceptibles aux fuites d'informations sur la mémoire d'un GPU.

# Abstract

In a virtualized environment, the hypervisor provides isolation at the software level, but shared infrastructure makes attacks possible at the hardware level. Side and covert channels are well-known issues of shared hardware, and in particular shared processors. However, they rely on microarchitectural features that are changing with the different generations of hardware. The last years have also shown the rise of General-Purpose computing on Graphics Processing Units (GPGPU), coupled to so-called *cloud* environments. This thesis explores these recent evolutions and their consequences in terms of information leakage in virtualized environments. We first investigate the recent processor microarchitectures. Our first contribution is C5, a cross-core cache covert channel, evaluated between virtual machines. Following this work, our second contribution is the reverse engineering of the complex addressing function of the last-level cache of Intel processors, rendering the class of cache attacks highly practical. In the last part, we investigate the security of GPU virtualization. Our third contribution shows that virtualized environments are susceptible to information leakage from the GPU memory.

# Acknowledgments

Many friends, family members and colleagues supported me during my thesis. I am glad I know them, and these few words cannot express all my gratitude to them.

I am grateful to my thesis committee Thomas Jensen, Gildas Avoine, Jean-Pierre Seifert, Stefan Mangard and Pierre Paradinas, for accepting to come to Rennes for my defense and for their constructive questions and comments. I particularly thank Jean-Pierre Seifert and Gildas Avoine for taking the time to read the manuscript and providing feedback.

I sincerely thank my thesis advisors Aurélien Francillon, Olivier Heen and Christoph Neumann, who, contrary to what the formal title page says, equally advised my thesis. You gave me a great balance between guidance and freedom in my research, and also trusted me with my crazy cache attack ideas. Thank you for your patience, support and encouragements, especially during rough times. I really enjoyed working with you!

My time in Technicolor would not have been as enjoyable without my former and current colleagues. Thanks for the fruitful technical discussions or fun conversations over coffee and for the general good mood. Special thanks to Fabien for sharing joy, despair and rooibos, and good luck for the end of the ride! Also thanks to the friendly S3 team of Eurecom for receiving me for my short and sunny stays. Best wishes to all the former and current members.

I would like to thank Stefan Mangard who invited me at TU Graz, as well as the whole Secure Systems team for their warm welcome. I really enjoyed my stay there, and am happy to come back. I especially thank Daniel — it's been great working with you and I am glad we continue to do so. Also thanks for accepting to read parts of this manuscript. Many thanks to Maria and Raphael as well, who coped with a great deal of enthusiasm out of a few bit flips.

A lot of thanks to the great people that are my friends and family. My parents Françoise and Patrick provided a computer-friendly environment that filled my nerdy aspirations during my childhood and supported me during my studies and this thesis. My extended family, including my in-laws Soizik and Marc, was always kind and encouraging. My friends, whether working on their own theses or observing this strange world from outside, were incredibly supportive. You're too many to be listed here, but I feel lucky to have y'all in my life. Thanks for your support and help, and all the good times shared together.

Last but not least, I would like to thank my beloved husband, Erwan. Your constant support over the years has been exceptionally important to me. I never could have done it without you, and for this I am forever grateful. To many more adventures!

# Foreword

This manuscript presents the work realized during my CIFRE PhD at Technicolor and Eurecom. It is mainly based on the published articles [MNHF14, MNHF15, MLSN<sup>+</sup>15] for which I am the main author, and the pre-print [GMM15] written as a follow-up of my visit at TU Graz, for which I am a co-author. During my stay at Technicolor, I also contributed to the published article [MON<sup>+</sup>13] that is out of the scope of this thesis.

## List of publications

## **International conferences**

Clémentine Maurice, Nicolas Le Scouarnec, Christoph Neumann, Olivier Heen, and Aurélien Francillon. Reverse Engineering Intel's Last-Level Cache Complex Addressing Using Performance Counters. In *Proceedings of the 18th International Symposium on Research in Attacks, Intrusions and Defenses (RAID'15)*, November 2015.

Clémentine Maurice, Christoph Neumann, Olivier Heen, and Aurélien Francillon. C5: Cross-Cores Cache Covert Channel. In *Proceedings of the 12th Conference on Detection of Intrusions and Malware, and Vulnerability Assessment (DIMVA'15)*, July 2015. Best paper award.

Clémentine Maurice, Christoph Neumann, Olivier Heen, and Aurélien Francillon. Confidentiality Issues on a GPU in a Virtualized Environment. In *Proceedings of the 18th International Conference on Financial Cryptography and Data Security (FC'14)*, March 2014. Clémentine Maurice, Stéphane Onno, Christoph Neumann, Olivier Heen, and Aurélien Francillon. Improving 802.11 Fingerprinting of Similar Devices by Cooperative Fingerprinting. In *Proceedings of the 2013 International Conference on Security and Cryptography (SECRYPT'13)*, August 2013.

#### **Pre-print**

Daniel Gruss, Clémentine Maurice, and Stefan Mangard. Rowhammer.js: A Remote Software-Induced Fault Attack in JavaScript. In *arXiv*:1507.06955v1, July 2015.

#### Presentations

Clémentine Maurice. Information Leakage in Virtualized Environments: A Journey into GPU Memory and CPU Caches. Secure Systems group seminar, IAIK, TU Graz, Austria, June 2015.

Clémentine Maurice, Christoph Neumann, Olivier Heen, Aurélien Francillon. Information Leakage in Virtualized GPUs. Poster presented at Security and Privacy thematic day of Labex UCN, Sophia Antipolis, France, December 2013.

Clémentine Maurice, Christoph Neumann, Olivier Heen, Aurélien Francillon. Information Leakage in a GPU in a Virtualized Environment. Presentation at the Third Workshop on Storage and Cloud Computing, Rennes, France, November 2013.

#### Awards and grants

RAID student travel grant, November 2015.

DIMVA Best paper award, July 2015.

Funding by the COST Cryptacus to visit TU Graz for a Short Term Scientific Mission, June 2015.

Hardware donation of a GPU by NVIDIA, April 2013.

# 1

# Introduction

#### Contents

| 1.1 | Context                    | 1 |

|-----|----------------------------|---|

| 1.2 | Problem statement          | 2 |

| 1.3 | Contributions              | 3 |

| 1.4 | Organization of the thesis | 5 |

## 1.1 Context

*Cloud computing* was introduced this last decade and gained in popularity ever since. It provides customers – users or enterprises – on-demand solutions for computing and storage in dedicated datacenters. For customers, the benefit is simplicity: the same services run on different hardware platforms, without having to consider the specificities of hardware. It also offloads the need to manage an infrastructure to a dedicated provider. For cloud providers, the benefit is cost efficiency: several virtual machines, that can be owned by different customers, run on the same physical machine. Cloud computing relies heavily on *virtualization*, which consists in the decoupling of software services from underlying hardware. Hardware sharing is a central aspect of the cloud computing environment. Among others, two important pieces of hardware are virtualized today: the Central Processing Unit (CPU), and the Graphics Processing Unit (GPU).

#### 1. Introduction

The CPU is the computing part of a computer system. As predicted by Moore's law [Moo75], x86 processors that constitute personal computers and servers become smaller, faster, and more power-efficient. The speed of the processor has increased exponentially over the last decades. Modern CPUs are composed of several cores, that are basic processing units. They also use *caches*, that are small but fast memories filling the performance gap between the processor and the main memory.

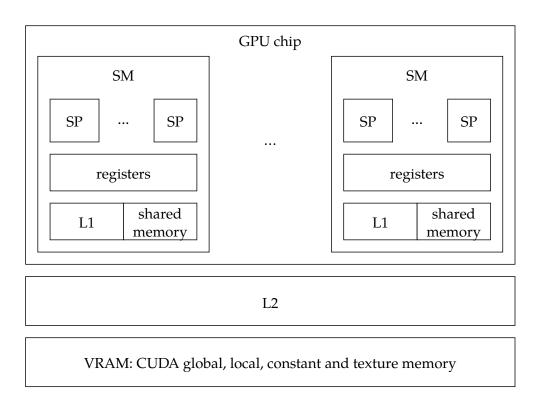

The GPU is used primarily in personal computers for multimedia applications such as video gaming or high-definition video editing. As these new multimedia usages grew, GPUs became widespread. Their highly parallel architecture changed towards general purpose computing. Today, GPUs are also used for high performance computing, including in servers and clusters. As a result, they made an appearance in services offered by cloud computing providers.

Shared hardware between different tenants induces the potential threat of information leakage. In particular, the CPU can be accessed concurrently by different users, and the CPU cache is heavily shared. This leads to *covert* and *side channels*. The GPU is time-shared, *i.e.*, not two users can access it at the same time, but they can access it one after the other. Memory isolation is crucial in this case to prevent information leakage. Attacks on these systems either aim to actively exchange information between two processes, or for a spy process to exfiltrate secret information from a victim process.

#### **1.2 Problem statement**

Information leakage due to shared hardware is a known problem and has been extensively studied. However, these attacks are highly dependent on the hardware. Yet, we see evolutions both in hardware design and adoption. First, CPU microarchitectures change frequently. For example, Intel has built a new one nearly every year since 2009. Second, GPUs have been designed to provide maximum performance and not for concurrent accesses and security. Nonetheless, they have been recently offered by several cloud computing providers. Due to the evolution of hardware or to the countermeasures in production, some attacks are rendered more complex or impossible to perform. In contrast, some modifications are carried out with performance in mind, which is often conflicting with security. We therefore question: *How do the recent evolutions impact information leakage due to hardware sharing*?

This question gives rise to some challenges concerning the investigation of these security issues. Indeed, we are faced with two layers of obscurity. The first is the cloud provider. For reasons as diverse as security concerns or business model, cloud providers are reluctant to give details about their infrastructure. The second is the hardware itself. As it is increasingly complex, both CPUs and GPUs are built with some performance-critical parts that remain undocumented.

## 1.3 Contributions

The goal of this thesis is to study the impact of evolutions in recent hardware in terms of information leakage on shared hardware. We also apply our findings to virtualized environments which are widely used today, and which constitute a natural use case of hardware sharing. This thesis presents the work done during my PhD and makes contributions along three axes.

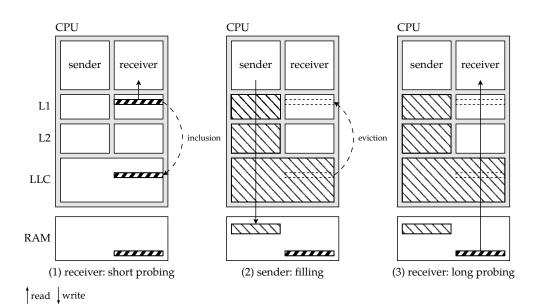

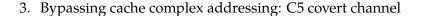

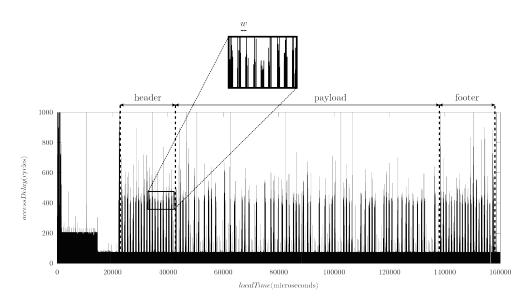

Building a Cross-Core Cache Covert Channel Covert channels were demonstrated to violate isolation and, typically, allow data exfiltration. Several covert channels have been proposed that rely on the CPU cache. However, these covert channels are either slow or impractical due to the *addressing uncertainty*. This uncertainty is caused by the additional layer of indirection in virtualized environment, and by the addressing mode of recent last-level caches. Using shared memory would elude addressing uncertainty, but shared memory is not available in most practical setups. We build C5, a covert channel that tackles addressing uncertainty without requiring any shared memory, making this covert channel fast and practical. We are able to transfer messages on modern hardware across any cores of the same processor. The C5 covert channel targets the last-level cache that is shared across all cores. It exploits the inclusive feature of caches, allowing a core to evict lines in the private first level cache of another core. We experimentally evaluate our covert channel in native and virtualized environments. In particular, we successfully establish a covert channel between virtual machines running on different cores. We measure a bitrate one order of magnitude above previous cache-based covert channels in the same setup.

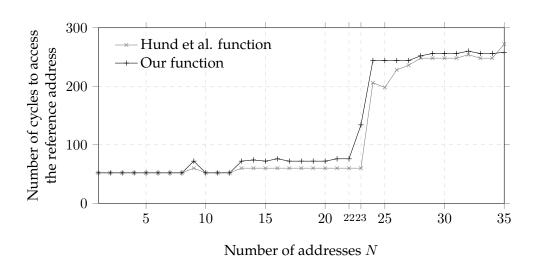

**Reverse-engineering the complex addressing function of Intel last-level cache** The last-level cache of recent processors is split in *slices*. While predicting the slice used by an address is simple in older processors, recent processors are using an undocumented technique called *complex addressing*. This renders some attacks more difficult and makes other attacks impossible, because of the loss of precision in the prediction of cache collisions. Previous work only

#### 1. Introduction

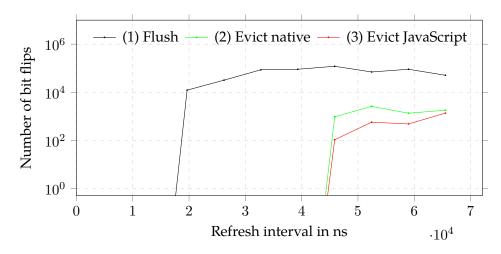

manually reverse-engineered the complex addressing function of one specific processor. We build an automatic and generic method for reverse-engineering Intel complex addressing, consequently rendering the class of cache attacks highly practical. Our method relies on CPU hardware performance counters to determine the cache slice an address is mapped to. We show that our method gives a more precise description of the complex addressing function than previous work. We validated our method by reversing the complex addressing function on a diverse set of Intel processors. This set encompasses Sandy Bridge, Ivy Bridge and Haswell microarchitectures, with different number of cores, for mobile and server range processors. We show that knowing the complex addressing function of a cache enables other attacks, such as sandboxed Rowhammer.

Information leakage on GPU memory in virtualized environments Few studies have been conducted on the security implications of General-Purpose Computing on Graphics Processing Units (GPGPU) combined to cloud computing. Our objective is to highlight possible information leakage due to GPUs in virtualized and cloud computing environments. We provide insight into the different GPU virtualization techniques, along with their security implications. We systematically experiment and analyze the behavior of GPU global memory in the case of direct device assignment. We find that GPU global memory is zeroed only in some configurations, as a side effect of Error Correction Codes (ECC) and not for security reasons. As a consequence, an attacker can recover data of a previously executed GPGPU application in a variety of situations. These situations include setups where the attacker launches a virtual machine after the victim's virtual machine using the same GPU, thus bypassing the isolation mechanisms of virtualization. Memory cleaning is not implemented by the GPU card itself and we cannot generally exclude the possibility of data leakage in cloud computing environments. Furthermore, we discuss possible countermeasures for current GPU clouds users and providers. To the best of our knowledge, this is the first work on information leakage of GPU memory in virtualized environments.

Our contributions in the domain of CPU cache covert channels make a significant advancement in two directions. First, by building a covert channel, we analyze the root causes of the interferences that make information leakage possible in recent processors. Second, the reverse engineering of Intel last-level

cache complex addressing function tackles one of the challenges that is the lack of documentation of hardware. Finally, our contribution in the domain of GPU memory isolation paves the way to secure virtualization of GPUs.

## 1.4 Organization of the thesis

This thesis is organized as follows.

- **Chapter 2** reviews technical background and the state of the art. It first covers the architecture and virtualization of x86 systems. It also includes information leakage on shared resources such as the memory bus and the CPU, with a focus on CPU caches and GPU memory.

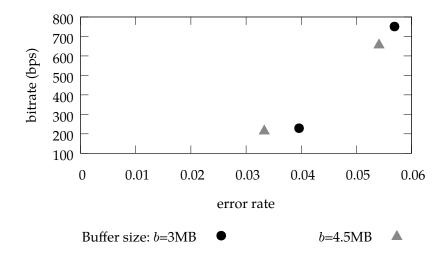

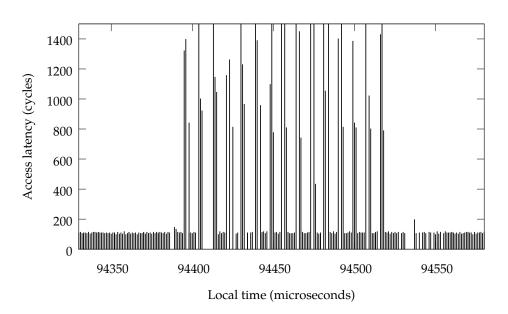

- **Chapter 3** presents C5, a new covert channel on inclusive last-level caches. This covert channel takes into account the evolution of recent CPUs. We evaluated its bitrate and error rate on setups across cores and across virtual machines.

- **Chapter 4** details how we reverse-engineered the complex addressing function of recent Intel last-level caches. We evaluated our approach by retrieving the function on a large set of different processors. We also show some security applications that ensued this work.

- **Chapter 5** documents the impact of GPU virtualization techniques on security. We systematically investigate information leakage on GPU memory, in particular in virtualized environments. We detail two methods to access GPU memory, that require different levels of privileges.

- Chapter 6 concludes and gives perspective on future work.

2

# State of the art

#### Contents

| 2.1 | Architecture of an x86 system                | 7  |

|-----|----------------------------------------------|----|

| 2.2 | Hardware virtualization                      | 13 |

| 2.3 | Covert and side channels on shared resources | 18 |

| 2.4 | The case of the data cache of x86 processors | 23 |

| 2.5 | Information leakage on GPU memory            | 33 |

| 2.6 | Conclusions                                  | 36 |

This chapter first introduces the architecture of an x86 system (Section 2.1), and in particular the internals of the CPU cache. We then detail hardware virtualization, concerning the CPU, memory and I/O devices, and the different threats in terms of security (Section 2.2). We next present covert and side channels on shared resources (Section 2.3), with a focus on the case of data cache (Section 2.4). Finally, we discuss information leakage on GPU memory (Section 2.5).

## 2.1 Architecture of an x86 system

## 2.1.1 CPU

A CPU is a component with one or more processing units called cores. Cores execute the sequence of instructions formed by programs. In this thesis, we focus on the Instruction Set Architecture (ISA) x86, that is present in most

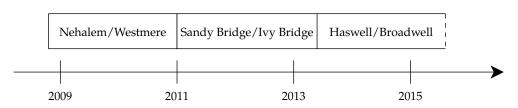

Figure 2.1: Timeline of the different Intel microarchitectures since Nehalem to the most recent one Broadwell.

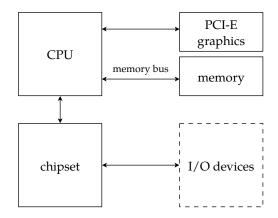

Figure 2.2: Baseline architecture of an x86 system.

personal computers and servers. The ISA can be implemented by a variety of *microarchitectures*. In this thesis, we focus on Intel processors as Intel has a dominant position in market share [For14], compared to AMD. Still, most of this discussion applies also to other x86 processors. Figure 2.1 shows the timeline of the most recent x86 Intel microarchitectures. Figure 2.2 illustrates the baseline architecture and different components of an x86 system.

Major microarchitectural advances in recent processors in terms of performance comprise: pipelining, out-of-order execution, speculative execution, multiple cores and threads, prefetching and caching. In pipelined processors, several instructions can be processed simultaneously, *i.e.*, in a single cycle, at different stages. This increases instruction-level parallelism. In out-of-order processors, the instructions can be processed in an order that is different from the one in the binary, depending on the availability of input data. With speculative execution, the processor performs a task before it is known if the task is actually needed. Intel started manufacturing multi-core processors in 2006; they are now widespread.

| core 0         | core 1         | core 2         | core 3         |  |  |  |  |

|----------------|----------------|----------------|----------------|--|--|--|--|

| L1             | L1             | L1             | L1             |  |  |  |  |

| L2             | L2             | L2             | L2             |  |  |  |  |

| ring bus       |                |                |                |  |  |  |  |

| LLC<br>slice 0 | LLC<br>slice 1 | LLC<br>slice 2 | LLC<br>slice 3 |  |  |  |  |

Figure 2.3: Cache hierarchy on Intel processors since Nehalem microarchitecture to the most recent one Broadwell.

We now describe in more detail cache organization, as well as branch prediction.

#### 2.1.1.1 Data cache

Data caches store recently-used data in a fast but small Static Random Access Memory (SRAM). They exploit the concepts of temporal and spatial locality: if some resource is accessed, it is likely to be re-accessed in the near future (temporal), as well as its neighbor resources (spatial).

**Cache hierarchy** Intel processors use a cache hierarchy similar to the one depicted in Figure 2.3 since the Nehalem microarchitecture and until the most recent Broadwell microarchitecture [Int14a]. There are usually three cache levels, called L1, L2 and L3. The levels L1 and L2 are private to each core, and store several kilobytes. The L3 cache is also called Last-Level Cache (LLC). It is shared among cores and can store several megabytes.

To read or write data in main memory, the CPU first checks the memory location in the L1 cache. If the address is found, it is a *cache hit* and the CPU immediately reads or writes data in the cache line. Otherwise, it is a *cache miss* and the CPU searches for the address in the next level, and so on, until reaching main memory. A cache hit is significantly faster than a cache miss.

**Particularities of the last-level cache in recent processors** In recent Intel processors, the last-level cache is divided into slices that are connected to the cores through a ring interconnect. Moreover, the last-level cache is inclusive,

#### 2. State of the art

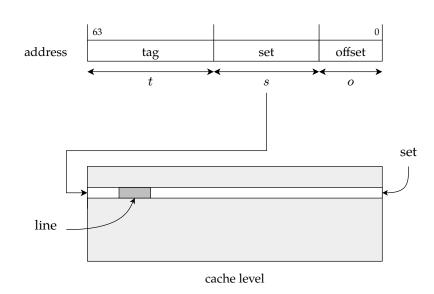

Figure 2.4: Simple addressing scheme.

which means that it is a superset of the L1 and L2, *i.e.*, it contains all data present in L1 and L2. This property does not fully exploit the total available capacity of the cache levels, however, it is an advantageous design for performance reasons, as only one level needs to be checked to know if a line is cached. Inclusiveness also simplifies the cache coherence protocol. To guarantee the inclusion property, a line evicted from the last-level cache is also removed (invalidated) in the L1 and L2 caches.

Addressing scheme Data is transferred between the cache and the memory in 64-byte blocks called *lines*. The location of a particular line depends on the cache structure. Today's caches are *n*-way associative, which means that a cache is composed of sets of n lines. A line is loaded in a specific set depending on its address, and occupies any of the n lines.

With caches that implement a *direct addressing* scheme, memory addresses can be decomposed in three parts: the tag, the set and the offset in the line. The lowest *o* bits determine the offset in the line, with:  $o = \log_2(\text{line size})$ . The next *s* bits determine the set, with:  $s = \log_2(\text{number of sets})$ . And the remaining *t* bits form the tag. Figure 2.4 illustrates this scheme.

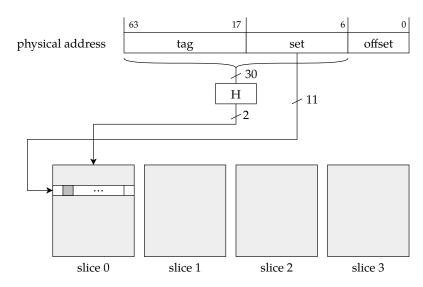

In contrast to direct addressing, some caches implement a *complex addressing* scheme, where potentially all address bits are used to index the cache. Indeed, in the last-level cache each physical address is associated with a slice via a function that is not documented by Intel, to the best of our knowledge.

Figure 2.5: Complex addressing scheme on the LLC. This assumes a quad-core processor, and the following characteristics of the LLC: 64B lines and 2048 sets per slice.

As each slice has a cache pipeline, the addressing function is designed to distribute evenly the traffic across all slices for a wide range of memory access patterns, to increase performance. The set is then directly addressed. Intel started implementing this complex addressing scheme on the Sandy Bridge microarchitecture, and onwards (see Table 2.1). Figure 2.5 illustrates this scheme.

The address used to compute the cache location can be either a physical or a virtual address. A *Virtually Indexed, Virtually Tagged* (VIVT) cache only uses virtual addresses to locate data in the cache. Modern processors involve physical addressing, thus cache levels are either *Virtually Indexed Physically Tagged* (VIPT), or *Physically Indexed Physically Tagged* (PIPT). The physical address is not known by processes, thus a process cannot know the location of a specific line for physically indexed caches. Typically, the L1 cache is VIPT, and L2 and L3 are PIPT.

**Replacement policy** When a cache set is full, a cache line needs to be evicted before storing a new cache line. When a line is evicted from L1 it is stored back to L2, which can lead to the eviction of a new line to the last-level cache, etc. The replacement policy decides the victim line to be evicted. Good replacement policies choose the line that is the least likely to be reused. Used policies include

Table 2.1: Characteristics of the recent Intel microarchitectures.

|                           | Nehalem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Sandy Bridge | Ivy Bridge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Haswell               |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| LLC slices                | <ul> <li>Image: A set of the set of the</li></ul> | ✓            | ✓                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <ul> <li>✓</li> </ul> |

| LLC complex addr.         | ×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ✓            | <ul> <li>Image: A second s</li></ul> | 1                     |

| <b>Replacement policy</b> | LRU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | LRU          | Quad-Age                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Quad-Age              |

Pseudo Random, Least Recently Used (LRU), and variations of LRU [JTSE10] (see Table 2.1). An adaptive policy can also be used, where the processor dynamically changes the replacement policy depending on the miss rate of specific cache sets [QJP<sup>+</sup>07]. An efficient replacement policy minimizes the number of cache misses and is thus crucial for performance. These policies are therefore not well documented in recent processors. For instance, the replacement policy used in the Ivy Bridge microarchitecture, a variation of LRU called Quad-Age, only appears as a part of an Intel presentation [JGSW], and is not fully documented to the best of our knowledge. Details of the replacement policies can however be partially reverse-engineered using microbenchmarks, as it has been done for the Ivy Bridge microarchitecture [Won13].

#### 2.1.1.2 Instruction cache

Similarly to the data cache, the instruction cache stores the most recently used program instructions, and benefits from temporal and spatial locality.

Recent Intel processors have an instruction cache that is private to each core and separate from the data cache for the L1. The L2 and L3 caches are unified, which means that they contain both data and instructions. All considerations we discussed for data caches apply to the instruction cache as well.

#### 2.1.1.3 Branch prediction unit

Two-way branches, e.g., an if-then-else structure, is usually implemented with a conditional jump instruction. The conditional jump can either be "taken" or "not taken". This cannot be known for sure until the condition has been calculated, which results in wasted cycles in the pipeline if the processor is stalling, waiting for it. Instead, speculative execution is used to improve performance.

The branch predictor predicts the outcome of the branch instructions, using past behavior. Thereby, the processor speculatively continues to execute instructions on the predicted path, without waiting for the outcome to be computed. When a misprediction happens the pipeline is flushed, thus all the speculative instructions have to be dumped and the execution has to start over, resulting in a longer execution time. The penalty depends on the length of the pipeline: the deeper the pipeline, the higher the penalty. Modern processors tend to have longer pipelines, thus the branch predictor is a critical element of modern pipelined processors.

If a branch is predicted to be taken, the next instruction needs to be fetched and issued. This requires knowing the address of this instruction. For that, the CPU uses a Branch Target Buffer, that is the buffer of the target addresses of previously executed branches. The Branch Target Buffer is a cache.

#### 2.1.2 Memory

The main memory (also referred simply as *memory*) is a volatile type of storage, *i.e.*, information is lost when memory is powered off, typically made of Dynamic Random Access Memory (DRAM). Contrary to external memory, e.g., hard disk drives, the main memory is directly accessible by the CPU, via the memory bus.

The memory bus connects the main memory to the memory controller. In recent CPUs, the memory controller has been moved from the motherboard to the CPU itself. It is called an integrated memory controller. The memory bus is actually composed of two different buses: the address bus and the data bus. The CPU sends the address on the address bus, to indicate the location of the requested data, and read or written data is sent via the data bus.

Modern CPUs implement virtual memory using a Memory Management Unit (MMU), a hardware unit between the CPU and the DRAM that maps virtual addresses used by processes to physical addresses.

#### 2.2 Hardware virtualization

Virtualization is the decoupling of software services from the underlying hardware. This solution has gained attraction, with the rise of the *cloud computing*. For users, the benefit is simplicity: the same services run on different hardware platforms, without having to consider the specificities of the hardware. For cloud providers, the benefit is cost efficiency: several Virtual Machines (VMs), that can be owned by different tenants, run on the same physical machine.

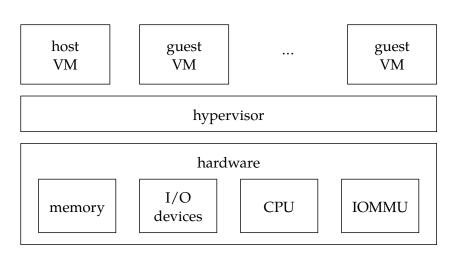

Virtualized environment have three main components: the *hypervisor* that is the abstraction layer, a *host operating system* that has privileged access to hardware, and *guest operating systems* that are unprivileged virtual machines. There are two main types of hardware virtualization. *Type 1* hypervisors, also called native or bare-metal, run directly on top of hardware (see Figure 2.6).

#### 2. State of the art

Figure 2.6: Type 1 virtualization.

They manage all the resources, including the CPU, memory and Input/Output (I/O) devices. Examples of type 1 hypervisors include Xen [BDF<sup>+</sup>03], KVM [KKL<sup>+</sup>07] and VMware ESXi. *Type* 2 hypervisors, also called hosted, run as a process on top of a host operating system. They manage access to hardware from the guest operating systems via calls to the host operating system. Examples of type 2 hypervisors include VMware Player and VirtualBox. In both types of virtualization, the crucial role of the hypervisor is to isolate the different guest operating systems from each other. Type 1 virtualization is the most used in multi-tenants environments such as in cloud computing environments. This is the type of virtualization we focus on in the remainder of this thesis.

#### 2.2.1 CPU

The x86 architecture provides some challenges to virtualization. Indeed, some sensitive instructions do not have the same semantics when executed in Ring 3 (least privileged, user-level application) and in Ring 0 (most privileged, kernel-level).

Software-based virtualization techniques include binary translation and para-virtualization. In *binary translation*, the hypervisor translates the virtual machine instructions before their execution. It replaces non-virtualizable instructions by instructions that behave the same way, but that do not have the same effect on the underlying hardware. Hardware is fully virtualized and the operating system that runs on top of it does not have to be adapted. To increase performance, a combination of binary translation for kernel-level code and direct execution for user-level code can be used. In *para-virtualization*, a virtualization layer that is similar to the underlying hardware is presented to the virtual machines. The operating system kernel is modified to replace non-virtualizable instructions by hypercalls (requests of privileged operations from a domain to the hypervisor).

*Hardware-based virtualization* was introduced by Intel and AMD in 2005 and 2006 – respectively named Intel VT-x and AMD-V. It extends the instruction set and creates a new ring for the hypervisor below Ring 0. It allows running an unmodified guest operating system that is unaware of the virtualization layer. When the processor encounters a privileged instruction, it *exits* from the guest mode, lets the hypervisor emulate the instruction, and then returns to the guest mode.

#### 2.2.2 Memory

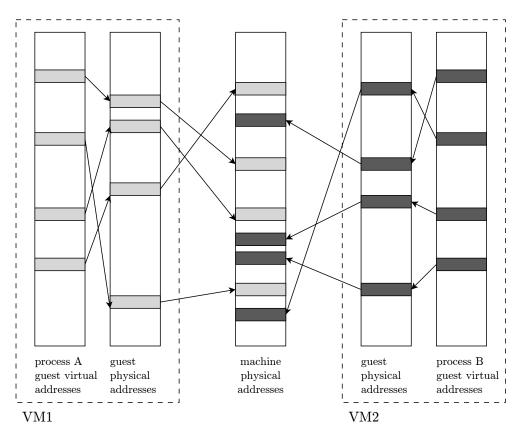

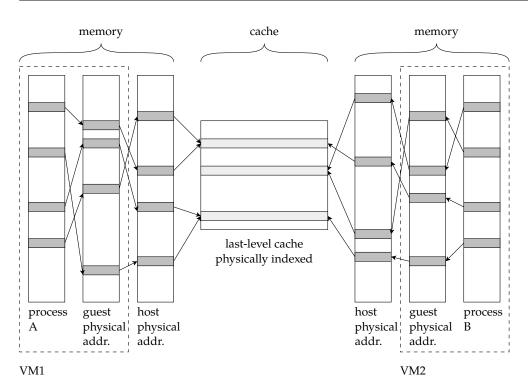

Memory virtualization handles an additional layer of indirection caused by the MMU: from the guest virtual pages, to the guest physical pages, to the actual machine pages (see Figure 2.7). The hypervisor is responsible to map the guest physical memory to the actual machine memory. To avoid performance penalty, software and hardware methods remove this additional layer of indirection.

With a software-based solution, the hypervisor maintains a shadow page table to directly map the guest virtual memory to the machine memory. However, the monitoring of the guest pages by the hypervisor entails a significant overhead. Indeed, the entries of the shadow page table are built at every guest page fault, which causes a hypervisor exit.

Intel and AMD brought hardware support for MMU virtualization, respectively named EPT (Extended Page Tables) and RVI (Rapid Virtualization Indexing). The guest continues to maintain guest virtual pages to guest physical pages mapping, but the guest physical pages to machine pages mapping is maintained by the hypervisor and exposed to hardware. The physical CPU walks the two tables and caches the guest virtual pages to machine pages mapping in the Translation Lookaside Buffer (TLB). Performance gain is evaluated to more than 40% compared to the software table [VMw09a, VMw09b].

Figure 2.7: Memory virtualization.

#### 2.2.3 I/O devices

Beyond the CPU and memory, a virtual machine needs to access I/O devices, such as Network Interface Cards (NICs) and Graphics Processing Units (GPUs). When virtualizing I/O devices, the hypervisor needs to route I/O requests of guests between the virtual device and the physical device.

With the *emulation* solution, the hypervisor has a software implementation of the features of standard devices, over any physical device. All the commands of the real-world device are replicated in software, and have the same behavior as its hardware counterpart. The common approach is to emulate a wellknown real-world device. This way, the guest operating system can run an unmodified device driver. This approach has acceptable performance for basic and low-bandwidth devices.

A *split-driver* (also called *paravirtualized driver*) solution lets a privileged domain handle hardware management. A frontend driver runs in the guest

virtual machine and forwards calls to the backend driver in the host. The backend driver then takes care of sharing resources among virtual machines. This solution requires special drivers for the guest virtual machine. However, it has the advantage of multiplexing several guests on the same hardware device, and improves performance compared to emulation.

With the *direct device assignment* solution, the guest virtual machine has direct control of the device. This is essentially achieved by mapping device memory into the virtual machine memory space. This solution requires dedicated hardware to limit the memory accesses of the device, and to re-route interrupts. It also forbids multiplexing, allowing a single guest on a given device. However, it does not require any driver change to the guest, and provides near native performance. It is thus an interesting solution for devices that have complex drivers, and are performance-oriented, such as GPUs.

*Single Root I/O Virtualization* (SR-IOV) capable devices can expose themselves to the operating system as several devices. With this solution, the hardware device itself can be composed of several independent functions (multiple devices) or multiplex the resources in hardware.

#### 2.2.4 Attack surface of the virtualization layer

The virtualization layer itself is a target, given its privileged access to hardware. The virtualization layer is composed of the hypervisor, the host operating system, as well as an emulator. This layer is quite complex and forms a large trusted computing base. The attacker searches to attack another guest by escaping the guest environment, targeting the hypervisor and performing his attack through privileged access via the host.

#### 2.2.4.1 Hypervisor

Hypervisor exits constitute a first attack surface. They are performed when the guest is interrupted so that the hypervisor handles an event. As Szefer et al. [SKLR11] noted, a guest performs a lot of exits: ~600 per second when idle, and more than 9 million when the guest starts. Each exit is a possibility for exploiting a bug in the hypervisor code. Typical proposed mitigations consist in reducing the trusted computing base. Seshadri et al. [SLQP07] proposed SecVisor, a hypervisor with a tiny code base. However, the lack of functionalities do not make it a practical alternative for cloud providers. Szefer et al. [SKLR11] proposed to remove the hypervisor attack surface altogether, by enabling guests to run natively on hardware, and eliminate all interactions between the hypervisor and guests.

#### 2.2.4.2 Device emulator

Virtual hardware, e.g., virtual network devices, are handled by an emulator such as QEMU. However, the code base of QEMU is hard to maintain: it includes many legacy devices, and low-level code. Vulnerabilities are thus regularly found. As an example, in 2015 Jason Geffner found a vulnerability in the virtual floppy disk controller [CVE15], making possible a privilege escalation regardless of the presence and configuration of the virtual floppy disk. The OpenStack Foundation [Ope13] recommended removing unused components from the system in order to minimize the QEMU code base as a practical defense.

#### 2.2.4.3 Direct device assignment

Physical hardware accessed by direct device assignment also introduces security issues. Certain hardware devices use Direct Memory Access (DMA) to access memory in the operating system in native environments. Arbitrary memory accesses are an issue in virtualized environments because it allows the guest to map its device memory into the memory of the host or into that of other guests. Pék et al. [PLS<sup>+</sup>14] reviewed these attacks and their feasibility. A hardware I/O Memory Management Unit (IOMMU), such as Intel's VT-d, thwarts DMA attacks by preventing devices from accessing arbitrary parts of the physical memory. However, Wojtczuk and Rutkowska showed that the IOMMU is not exempt from vulnerabilities by building software attacks that bypass it [WR11]. Willmann et al. [WRC08] reviewed different protection strategies for devices in direct device assignment. They argue that softwareonly strategies can outperform IOMMU-based strategies, with less overhead.

## 2.3 Covert and side channels on shared resources

We now consider another type of attacks, applicable more broadly to multitenant environments, for which virtualization is a natural use case. In the case of virtualization, these attacks do not rely on flaws in the virtualization layer such as described in Section 2.2.4. Instead of directly compromising the other guest, the attacker is a non-privileged process that uses shared hardware as a medium to leak information. These attacks fall into the category of *covert channels* and *side channels*. Covert channels involve the cooperation of two attacker processes to actively exchange information. Side channels imply passive observation of a victim process by an attacker process, usually to extract a secret like a cryptographic key.

#### 2.3.1 Achieving and detecting co-residency

To perform covert or side channels on shared hardware, the first step for an attacker is to be *co-resident* with his victim, *i.e.*, to share a physical machine. In a native environment, the attacker has to run a program on the same operating system as its victim. In a virtualized environment, the attacker has to run a virtual machine alongside the virtual machine of its victim, on the same physical machine. We now review methods for an attacker to achieve and detect co-residency on a virtualized environment.

Ristenpart et al. [RTSS09] presented some heuristics to achieve co-residency on Amazon EC2 instance placement. They started by mapping the IP ranges of EC2 service, that correspond to different instance types and availability zones. The authors also showed that a brute-force strategy already achieves a reasonable success rate, for a large set of victim instances. A more elaborate strategy abuses the placement algorithm, that tends to co-locate virtual machines launched in a short temporal interval. The attacker can also abuse the auto-scaling system that automatically creates new instances when demand increases. This forces the victim to launch a new instance, from which point the attacker can himself launch new instances until one is co-resident with the victim. Varadarajan et al. [VZRS15] reevaluated the co-residency vulnerability in three major cloud providers, after the adoption of Virtual Private Cloud (VPC). VPC logically isolates networks, but it does not gives physical isolation, *i.e.*, virtual machines from different VPCs can share the same physical machine. Varadarajan et al. found that VPC makes prior attacks ineffective. However, Xu et al. [XWW15] demonstrated a new approach to attack instances that are in a VPC. They exploit latency variations in routing between instances that are behind a VPC and instances that are not. This approach comes at high cost, as an attacker needs to launch more than 1000 instances to achieve co-residency in a VPC. However, it shows that virtual network isolation does not completely solve the issue, thus attacks on co-resident virtual machines are still a real threat.

The next step is then to check co-residency. In [RTSS09], the authors also proposed a load-based co-residency test based on requests of a client that performs HTTP requests. With their tool HomeAlone, Zhang et al. [ZJOR11] monitored L2 cache usage to detect co-residency: they used a classical side channel as a defensive tool. A virtual machine that wants to attack a co-resident victim running HomeAlone has to lower its fingerprint, and consequently cannot use the cache as a side channel. Bates et al. [BMPP12] leveraged the sharing of the network interface to detect a co-resident virtual machine via traffic analysis techniques. The attacker needs a flooder virtual machine and a client that makes requests to a victim server. If the flooder is co-resident with the victim server, the flooder can induce a watermark, *i.e.*, a specific pattern, in the traffic from the victim server to the client.

#### 2.3.2 Attack surface of an x86 processor

#### 2.3.2.1 Data and instruction cache

Side and covert channels on both data and instruction caches are based on differences in timing between memory accesses that are in cache, and ones that are served from the main memory.

Data cache attacks exploit secret-dependent data access patterns. They happen when the implementation of cryptographic algorithms relies on lookups that depend on the secret key – e.g., the substitution boxes in block ciphers such as AES, and the multipliers table in public-key algorithms such as RSA. There is a large body of literature on the subject of data cache attacks. These attacks are described in more detail in Section 2.4.

Instruction cache attacks exploit secret-dependent execution paths instead. They work similarly as data cache attacks. Block ciphers like AES are not vulnerable to instruction cache attacks since they have a fixed instruction flow. Aciiçmez [Aci07] used the instruction cache to attack RSA implementations that use Square and Multiply exponentiation algorithm. The sequence of square and multiply operations are key-dependent. A spy process executes dummy instructions to fill the cache before the execution of the cipher process. If the cipher process executes square (resp. multiply) instructions, it evicts the dummy instructions of the attacker, which will result in a cache miss when the attacker resumes the execution of his dummy instructions. The attacker thus reveals the execution flow of the cipher by measuring the execution time of his own instructions. Aciiçmez et al. [ABG10] later improved the method using supervised learning. Zhang et al. [ZJRR12] demonstrated the attack across different virtual machines on Xen hypervisor to extract ElGamal decryption keys.